- 您现在的位置:买卖IC网 > Sheet目录327 > HW-V4-ML410-UNI-G-J (Xilinx Inc)EVALUATION PLATFORM VIRTEX-4

R

Detailed Description

PCI Express

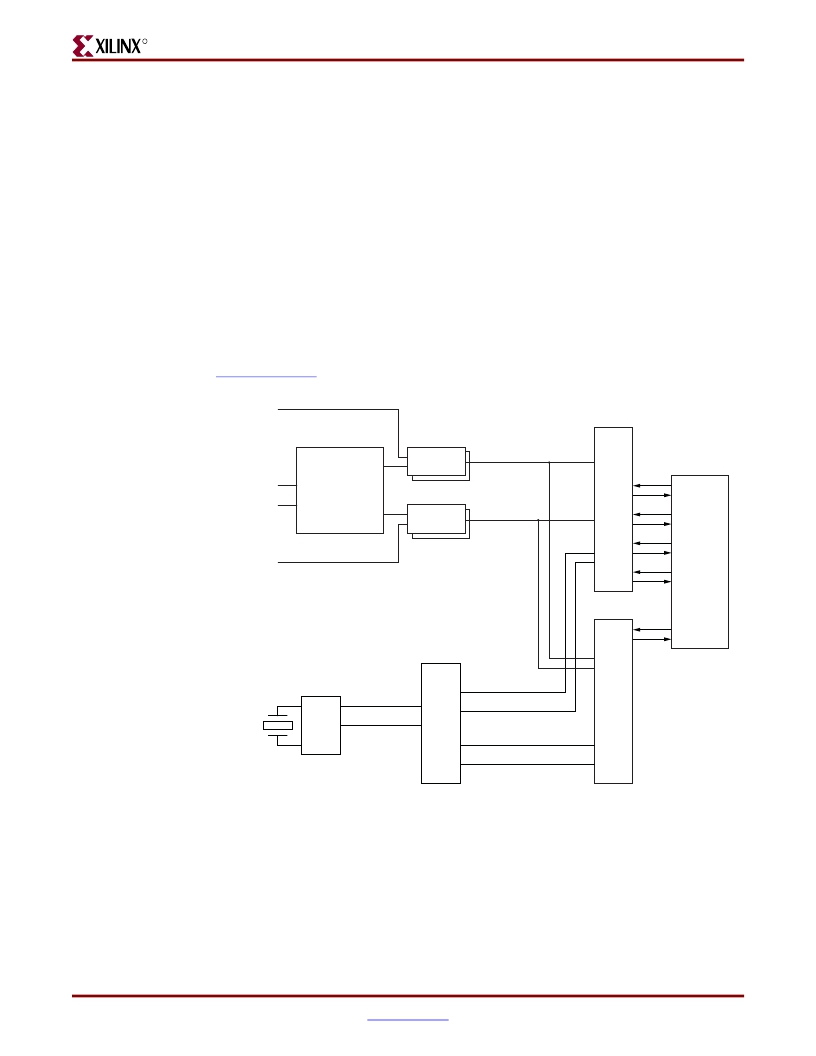

ML410 platforms that are equipped with PCI Express host connectors (P53 and P54) are

capable of supporting PCI Express cores. Power distribution is handled by a MIC2959B

dual-slot PCI Express hot-plug controller ( Figure 2-16 ) that also provides comprehensive

system protection and fault isolation. The MIC2959B controls the power delivered through

MOSFETs to the Slot A (P53) and Slot B (P54) PCI Express connectors. The MIC2592B also

incorporates an SMBus interface that provides control for and status of each PCI Express

slot.

Although two 16x PCI Express connectors are mounted on ML410 platforms, not all 16

lanes are wired for use. Refer to Appendix A, “Board Revisions” for a summary of features

and devices available on each board.

The PCI Express interface supports MGTs operating at 2.5 Gb/s. Power is activated to the

PCI Express slots only when the proper MIC2959B IIC commands are delivered to the

MIC2959B at address 0x8E over the IIC interface. For more on IIC, see “IIC/SMBus

www.micrel.com . For more on clocking, see “Clock Generation,” page 26 .

+3.3

PCI Express

Power Management

PCIE Slot A

U51/U52

+3.3V @ 3A

FPGA (U37)

IIC_SCL

IIC_SDA

U55

ADDR: 0x8E

MOSFETs

U14/U16

+12V @ 2.1A

P53

MGT

MGT

MIC2592B

MGT

+12V

MGT

PCIE Slot B

MGT

XC4VFX60

CLK100_Q0

PCIE_SLOTA_CLK

PCIE_SLOTA_NCLK

P54

X5

25 MHz

U48

CLK100_NQ0

100 MHz

U53

100 MHz

PCIE_SLOTB_CLK

PCIE_SLOTB_NCLK

ICS874003

UG085_29_0526406

Figure 2-16:

PCI Express Power Management and Clocking

ML410 Embedded Development Platform

UG085 (v1.7.2) December 11, 2008

55

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

HW-V5-ML501-UNI-G

EVALUATION PLATFORM VIRTEX-5

HW-V5-ML507-UNI-G

EVAL PLATFORM V5 FXT

HW-V5-ML550-UNI-G

EVALUATION PLATFORM VIRTEX-5

HW-V5-ML555-G

BOARD EVAL FOR VIRTEX-5 ML555

HW-V5-ML561-UNI-G

EVALUATION PLATFORM VIRTEX-5

I-JET

JTAG ARM DEBUGGING PROBE

IAC24A

INPUT MODULE AC 5MA 24VDC

IAC5EQ

INPUT MODULE AC 10MA 5VDC

相关代理商/技术参数

HW-V4-ML423-UNI-G

功能描述:EVALUATION PLATFORM VIRTEX-4 RoHS:是 类别:编程器,开发系统 >> 过时/停产零件编号 系列:Virtex®-4 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP

HW-V4-ML423-UNI-G-J

功能描述:EVALUATION PLATFORM VIRTEX-4 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex®-4 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

HW-V4SX35-VIDEO-SK-EC

功能描述:VIRTEX-4 VIDEO STARTER KIT RoHS:否 类别:编程器,开发系统 >> 过时/停产零件编号 系列:Virtex®-4 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP

HW-V4SX35-VIDEO-SK-UK

功能描述:VIRTEX-4 VIDEO STARTER KIT RoHS:否 类别:编程器,开发系统 >> 过时/停产零件编号 系列:Virtex®-4 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP

HW-V5GBE-DK-UNI-G

功能描述:KIT DEV V5 LXT GIGABIT ETHERNET RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex®-5 LXT 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

HW-V5GBE-DK-UNI-G-J

功能描述:KIT DEV GIGABIT ETHERNET VIRTEX5 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex®-5 LXT 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

HW-V5GBE-DK-UNI-G-PROMO1

功能描述:KIT DEV V5 LXT GIGABIT ETHERNET RoHS:是 类别:编程器,开发系统 >> 过时/停产零件编号 系列:- 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP

HW-V5GBE-DK-UNI-G-PROMO2

功能描述:KIT DEV V5 LXT GIGABIT ETHERNET RoHS:是 类别:编程器,开发系统 >> 过时/停产零件编号 系列:Virtex® 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP